Revista Mexicana de Física

ISSN: 0035-001X

rmf@ciencias.unam.mx

Sociedad Mexicana de Física A.C.

México

Montoya-Suárez, E.; Sandoval-Ibarra, F.; Ortega-Cisneros, S.

Medición de temperatura usando un VCO integrado en silicio

Revista Mexicana de Física, vol. 57, núm. 6, diciembre, 2011, pp. 535-540

Sociedad Mexicana de Física A.C.

Distrito Federal, México

Disponible en: http://www.redalyc.org/articulo.oa?id=57021213011

Número completo

Más información del artículo

Página de la revista en redalyc.org

# Medición de temperatura usando un VCO integrado en silicio

E. Montoya-Suárez

Área de Ciencias Básicas e Ingenierías, Universidad Autónoma de Nayarit, Cd. de la cultura Amado Nervo, e-mail: emontoya@nayar.uan.mx

F. Sandoval-Ibarra y S. Ortega-Cisneros Cinvestav-Unidad Guadalajara, Av. Del Bosque 1145, Col. El Bajío, 45015 Zapopan, Jal. e-mail: Sandoval@gdl.cinvestav.mx; sortega@gdl.cinvestav.mx

Recibido el 2 de marzo de 2011; aceptado el 4 de noviembre de 2011

La frecuencia de oscilación  $f_0$  de un VCO *current-starved* es usada para sensar temperatura en el rango de 20 a 99°C. Debido a que la frecuencia  $f_0$  es directamente proporcional a la corriente de cortocircuito de la celda básica de construcción (compuerta NOT), y considerando que esta corriente,  $I_{SHORT}$ , es directamente proporcional a la movilidad de portadores, es posible explicar cómo es que  $f_0$  varía con cambios en la temperatura, T. El diseño del oscilador, manufacturado en una tecnología CMOS, pozo N, 0.5  $\mu$ m, 5V, permite su integración con circuitos digitales de acondicionamiento cuyo principio básico de operación es la medición de la frecuencia en intervalos de 53 ms; esta ventana de tiempo es resultado del ajuste lineal (con un coeficiente de correlación r=0.996) aplicado a la característica  $f_0$  vs. T.

Descriptores: Osciladores; teoría de circuitos; mediciones eléctricas; dispositivos de efecto de campo.

The oscillation frequency  $f_0$  of a VCO *current-starved* has been used for sensing temperature ranging from 20 to 99°C. Since  $f_0$  is directly proportional to the short-circuit current of the basic cell delay (NOT gate), and taking into account that this current,  $I_{SHORT}$ , is directly proportional to the carrier mobility, it is possible to explain how  $f_0$  changes as temperature, T, changes too. This oscillator that was manufactured in a CMOS standard process, N-well, 0.5  $\mu$ m, 5 V, facilitates the integration of circuitry conditioning, which means the feasibility of integrating the whole sensor system in a chip. Digital circuit measures the frequency  $f_0$  each 53 ms because the measure step is deduced from the linear fitting applied to the  $f_0$  vs. T characteristic.

Keywords: Oscillators; circuits theory; electrical measurements; field effect devices.

PACS: 84.30.Ng; 84.30. Bv; 84.37.+q; 85.30.Tv

#### 1. Introducción

En diversos campos de aplicación es común monitorear variables físicas, siendo una característica muy recurrente el desarrollo de métodos de medición que presenten una relación lineal con la variable física a medir. Del punto de vista del diseño electrónico, la búsqueda de relaciones lineales favorece que la circuitería de acondicionamiento no incluya técnicas para linealizar la curva característica, es decir, reducir la circuitería es una consideración deseable de diseño porque hoy día un alto porcentaje de los sistemas sensores se integran en tecnologías digitales. Si bien un desarrollo puede ser manufacturado en tecnologías híbridas, también es verdad que los sistemas completamente integrados en silicio son económicos [1]. Estas tecnologías, sin embargo, son mayoritariamente digitales y ello significa que la posibilidad de fabricar resistores u otras estructuras no estándar para monitorear variables físicas no es posible [2]. En contraste, están las tecnologías de fabricación de circuitos integrados (CIs) de señal mezclada, y en éstas tanto resistores como otros elementos sensores pueden ser fabricados. Otra ventaja de estas tecnologías es que puede desarrollarse en un mismo chip todo el sistema: el sensor y la circuitería de acondicionamiento. Por lo anterior, es propósito de esta contribución describir el método seleccionado para sensar temperatura y más específicamente para responder a la pregunta ¿es posible definir un procedimiento que cuantifique cambios de temperatura usando únicamente los elementos de red básicos de una tecnología digital de CIs en silicio?

A la par del desarrollo tecnológico, hacer mediciones de temperatura in situ ha sido intentado por otros autores que de una u otra manera han puesto en marcha diversas propuestas. Una de ellas, quizás la más tradicional, es usar un diodo como elemento sensor porque éste es compatible con las tecnologías de fabricación de CIs. La característica corrientevoltaje de este dispositivo, si bien tiende a una aproximación exponencial, también es cierto que el manejo de corriente es función del voltaje térmico, y en consecuencia de la temperatura, T. Un inconveniente de este componente, es que otro diodo con idénticas características debe ser usado como generador de una señal de referencia, lo que implica que no debe estar expuesto a efectos térmicos. Otra propuesta, que no demanda elementos de referencia, es esa que usa un transistor bipolar y donde la unión base-emisor necesariamente debe polarizarse en directa; la condición de polarización se logra al invectar una corriente muy específica. El principio básico de operación es simple, si dos corrientes son inyectadas,  $I_L$ e  $I_H$ , el voltaje  $V_{\rm BE}$  puede ser medido, y entonces la temperatura es cuantificada con una diferencia de voltaje según el siguiente modelo:

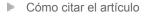

FIGURA 1. Oscilador de anillo formado por una compuerta NOT básica (a), y respuesta en el dominio del tiempo (b). Usando una compuerta NOT con control de  $I_{\rm SHORT}$  (c), la topología del oscilador no cambia.

$$T = \frac{q}{\eta K_B} \cdot \frac{V_{BEH} - V_{BEL}}{\ln \frac{I_H}{I_L}} \tag{1}$$

donde  $K_B$  es la constante de Boltzmann, q la carga eléctrica, y  $\eta$  es la constante del modelo exponencial del diodo [3]. Un inconveniente en esta propuesta es la dependencia con  $\eta$ , cuyo valor oscila entre 1 y 2, lo que hace de esta incertidumbre un factor negativo en la certidumbre de (1). En otras palabras, para evitar lecturas erróneas, cada unión debe ser caracterizada para conocer el valor particular de  $\eta$ . Por lo anterior la solución que se busca es aquélla que use un circuito que de manera intrínseca forme parte de las soluciones digitales integradas en silicio, que no requiera integrar el sensor y un elemento de referencia, ni tampoco un sensor cuya lectura dependa del conocimiento exacto de sus parámetros fundamentales, ni del efecto negativo de los componentes parásitos [4].

La solución que se propone, en esta contribución, es usar un oscilador controlado por voltaje (VCO por sus siglas en inglés) como sensor de temperatura. La razón es simple, un VCO se utiliza en una gran cantidad de aplicaciones digitales y usualmente se le encuentra embebido en la mayoría de los CIs, fundamentalmente para temporización [5]. Del punto de vista del diseño, un VCO es un circuito simple, y con las técnicas básicas de procesamiento digital es posible usarle como sensor de temperatura vía las variaciones en la frecuencia de oscilación; una propuesta así es un sensor que no usa mediciones de corriente y/o voltaje como las técnicas de sensado tradicionales [6].

Este artículo está estructurado de la siguiente manera. En la Sec. 2 se presenta el principio básico de operación de un VCO *current-starved*. También se presentan resultados experimentales de los osciladores fabricados en una tecnología estándar CMOS. La curva característica frecuencia-deoscilación como función de la temperatura se presenta en la Sec. 3, y donde una aproximación lineal es usada para modelar el desempeño del oscilador. El ajuste, si bien es válido en un rango específico del voltaje de control, permite monitorear un importante rango de temperatura. La arquitectura completa del circuito sensor, para propósitos de validación, se analiza en la Sec. 4, donde las lecturas se realizan en código BCD de dos dígitos con una resolución de 1°C en el rango

20-99°C. Conclusiones, áreas de aplicación, y una descripción de la aportación de este trabajo se presentan en la Sec. 5.

### 2. VCO current-starved

Este oscilador, que se construye a partir de una celda básica (compuerta NOT), es un circuito formado por la conexión sucesiva de un número impar de compuertas NOT, y en el que la respuesta  $V_O$  de la N-enésima compuerta es la excitación de la primera, de ahí que el circuito así formado sea un oscilador de anillo (ver Fig. 1). En la práctica, se sabe que la frecuencia de oscilación es función del número N de compuertas, a las que les caracteriza un retardo  $\tau_d \approx R_{\rm eq} C_p$  [7]. Consecuentemente, el modelo analítico que suele usarse para aproximar la frecuencia de oscilación está dada por

$$f_0 \approx \frac{1}{2NR_{eq}C_p} \tag{2}$$

Obsérvese que al usar este modelo se considera que el retardo es función de una capacitancia parásita  $C_p$ , y de una resistencia equivalente -que los autores asocian- a la transición lógica que experimenta la compuerta NOT, es decir, si la transición ocurre de  $V_{\rm DD}$  a  $G_{\rm ND}$  (o viceversa) los transistores  $(M_{p1} \text{ y } M_{n2} \text{ en la Fig. 1a})$  que forman la compuerta están en conducción, y ello significa que circula una corriente  $I_{SHORT}$ . Luego, si el punto medio de la transición se define en el potencial  $V_O = (1/2)(V_{\rm DD} - G_{\rm ND})$ , en conjunción con  $I_{\rm SHORT}$ se obtiene  $R_{\rm eq}$  vía la ley de Ohm. Esta definición invitaría, en primera instancia, a considerar la transición y más específicamente el cruce por  $(1/2)V_{\rm DD}$  como la métrica para estimar la frecuencia de oscilación. En la práctica, el cruce por  $(1/2)V_{\rm DD}$ no es garantía de que haya una señal oscilante cuya amplitud alcance los valores de polarización, es decir, para el procesamiento digital de señales es necesario que la amplitud de la señal de reloj alcance esos valores y que permanezca en ellos durante el tiempo establecido por el proceso de temporización; la Fig. 1b muestra la forma de onda generada por un oscilador de anillo. Por lo anterior, debe considerarse a (2) como una buena aproximación para estimar la frecuencia de oscilación de una onda cuadrada, fundamentalmente porque el diseño de la celda básica satisface que el tiempo de la transición bajo-alto sea aproximadamente igual al de la transición alto-bajo; ello justifica el factor 2 en (2) y (3). Otros autores, no obstante, omiten ese factor y consideran a  $C_p$  como la suma de una capacitancia  $C_{\rm out}$  (la parásita asociada al nodo de salida de la compuerta) y  $C_{\rm in}$  (la que corresponde al nodo de entrada de la compuerta). En tal situación, las transiciones alto-bajo y bajo-alto no son necesariamente de igual valor [4]. La Ec. (2), por otro lado, puede usarse también para describir de manera aproximada el desempeño de un oscilador de anillo controlado por voltaje. En esta clase de oscilador el objetivo es controlar la magnitud de  $I_{SHORT}$ :

$$f_0 \approx \frac{I_{\mathrm{SHORT}}}{2NV_{\mathrm{DD}}C_p}$$

(3)

Como se observa en la Fig. 1a, la compuerta NOT es la más simple implementación CMOS, y si bien la corriente  $I_{SHORT}$  influye en el retardo de la compuerta, también es verdad que su valor es definido cuando se establece la relación W/L de cada transistor; la corriente en un transistor MOS es directamente proporcional a la relación W/L, siendo W y L el ancho y longitud del canal, respectivamente. Obsérvese que  $f_0$  aumenta si  $I_{SHORT}$  incrementa su valor, y ello es posible si el ancho del canal W es de gran valor, o alternativamente si la longitud L se selecciona al mínimo definido por la tecnología (lo que es común en el diseño de celdas digitales); para la tecnología usada en esta contribución  $L_{\min}=3 \lambda$ , con  $\lambda=0.3 \mu m$ . En la práctica, hay otras opciones para controlar la magnitud de  $I_{SHORT}$ , siendo una de ellas la incorporación de transistores que hagan la función de fuentes de corriente. Esta compuerta NOT se muestra en la Fig. 1c, donde un voltaje  $V_{\text{CON}}$  se aplica a la compuerta del transistor  $M_{n4}$ . Nótese que, en la Fig. 1c, el circuito de polarización forma un espejo de corriente con cada compuerta NOT, es decir la magnitud de  $I_{SHORT}$  se controla con  $V_{CON}$ . Este oscilador es un VCO current-starved [5]. Obsérvese, por otro lado, que otra manera de incrementar la frecuencia de oscilación es reduciendo el valor de la capacitancia. Estrictamente hablando no hay un mecanismo para reducir ese valor, excepto si se diseña el VCO en una tecnología nanométrica. Para esas situaciones en el que se requiera una frecuencia de oscilación de varias centenas de MHz, o incluso del orden de GHz, se justificaría el uso de esas tecnologías. Si tal exigencia no existe, una tecnología micrométrica es adecuada para obtener un tren de pulsos bien definido, y ello tiene la ventaja de no incorporar en el diseño el efecto de las variaciones de los parámetros fundamentales de la tecnología, donde la densidad de dopantes, voltajes de encendido, y grosor del óxido son algunos de ellos [4]. Sin embargo, para otras aplicaciones que demanden frecuencias de oscilación de pocas decenas de GHz, puede optarse por un LC-VCO como el descrito en [8].

#### 2.1. Validación experimental

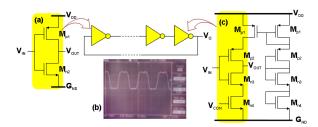

El VCO diseñado –completamente digital- con diferente número de etapas, fue manufacturado en un proceso estándar CMOS, 0.5  $\mu$ m, pozo N, 5-V. El chip de prueba se muestra en la Fig. 2a; la integración de los osciladores están indicados por un recuadro. Para propósitos de prueba, la señal de con-

FIGURA 2. Chip de prueba y ubicación de los VCO *current-starved* (a). Experimentalmente se ve que  $f_0$  aumenta para mayores valores de  $V_{\rm CON}$  (b).

trol se definió como una rampa de voltaje, con lo cual el aumento en la corriente debe reflejar un cambio en la frecuencia de oscilación. Es importante mencionar que el error entre los valores obtenidos con (3) y los datos experimentales es aproximadamente 3.47 % [9]. Si bien el error pudiera considerarse dentro del error propio del experimento (y no del método aplicado), también es verdad que los modelos analíticos de diseño –como las Ecs. (2) y (3)– solo representan una aproximación a la correlación que se desea.

La Fig. 2b muestra cómo conforme  $V_{\rm CON}$  incrementa su valor (lo que implica un aumento en la magnitud de  $I_{\rm SHORT}$ ) el periodo de la señal disminuye (o equivalentemente la frecuencia  $f_{\rm O}$  aumenta); la captura de datos experimentales se realizó a temperatura ambiente. Nótese que para todos los valores de  $V_{\rm CON}$  la respuesta es una onda cuadrada cuya transición alcanza los valores de alimentación. Para propósitos del sensado de temperatura se desea trasladar los datos experimentales al dominio de la frecuencia, de manera que con la característica  $f_{\rm O}$  vs  $V_{\rm CON}$  se determine el rango de dependencia lineal entre ambos parámetros.

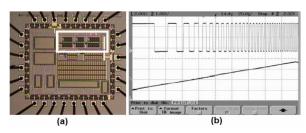

## 3. Desempeño en función de la temperatura

La solución (en *hardware*) que se presenta resulta de evaluar el desempeño de varios VCOs ante variaciones de temperatura, tanto a nivel simulación spice como en laboratorio (ver Fig. 3). El análisis de la información experimental, si bien permite corroborar la utilidad de (3) como modelo de diseño permite también el desarrollo de otros modelos analíticos – susceptibles de ser implementados en *software*— y que describan el desempeño experimental del VCO en función del número de etapas y de la temperatura [9]. La Fig. 3 muestra un ejemplo de la caracterización del circuito. Obsérvese que para cualquier número de etapas, es posible realizar un ajuste lineal que permita obtener un modelo analítico para  $f_{\rm O}$  como función de  $V_{\rm CON}$ . Obsérvese, por un lado, que la característi-

FIGURA 3. Respuesta experimental de VCOs *current-starved* para diferentes valores de temperatura.

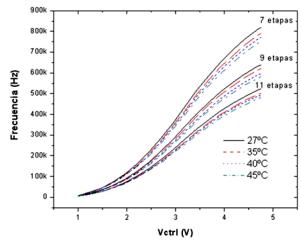

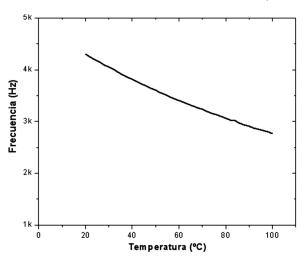

FIGURA 4. Desempeño del VCO  $\it current$ -starved como función de  $\it T$ .

ca  $f_O-V_{\rm CON}$  es no lineal, es decir, la variación de  $I_{\rm SHORT}$  no es proporcional a la variación de  $V_{\rm CON}$ .

Para justificar esa no linealidad téngase presente que en el desarrollo de (3) se asume que todo transistor opera en saturación. Esta premisa, sin embargo, no se cumple en esas situaciones en el que  $V_{\text{CON}}$  es menor al voltaje de encendido de  $M_{n4}$ ; esos transistores (uno por cada compuerta NOT) no solo no operan en saturación, sino que la inversión del canal no ha alcanzado el régimen de fuerte inversión; la densidad de carga en el canal del transistor, al pasar de débil a moderada inversión sigue una tendencia exponencial que se refleja en los valores de  $V_{\rm CON}$  poco mayores a 1V (ver Fig. 3). Cuando  $M_{n4}$  está en fuerte inversión el transistor pasa de la región lineal de operación a la de saturación, y entonces la corriente  $I_{SHORT}$  es aproximadamente proporcional a  $V_{CON}$ . Recuérdese, por otro lado, que la relación W/L de cada transistor es fija, es decir, la capacidad en el manejo de corriente es finita. Consecuentemente si  $V_{\rm CON}$  aumenta su valor ello implicaría un mayor manejo de corriente, pero ésta, al estar limitada por

el dimensionamiento de la compuerta NOT, tiende a saturarse aproximadamente para valores  $V_{\rm CON}>4$  V. Este comportamiento explicaría por qué la validez de (3) ocurre aproximadamente en el rango  $2V \le V_{\text{CON}} \le 4 \text{ V}$ . En tecnologías nanométricas, por ejemplo, se ha observado que la característica  $f_O - V_{\rm CON}$  obedece una tendencia lineal en una región muy pequeña de valores del voltaje de control [4]. En tal circunstancia o bien un circuito adicional es necesario para fijar el voltaje de control al valor deseado [10], o alternativamente se aprovechan aquellas variables que dan cuenta del aumento en temperatura, y que se usan para generar el voltaje de control del VCO [11]. Nótese, por otro lado, que conforme aumenta la temperatura se obtiene una reducción en la frecuencia de oscilación, es decir, este parámetro presenta dependencia con el recíproco de la temperatura,  $f_O \propto (T)^{-1}$ . Sin embargo el modelo deseado es ese que presente una dependencia proporcional a la temperatura. La Fig. 4 muestra la característica  $f_{\rm osc}$  vs. T en un VCO de once etapas; a temperatura ambiente  $f_{\rm osc}$ =4.1 kHz con  $V_{\rm CON}$ =5 V. Esta curva característica se obtuvo de simulaciones spice, realizando un barrido en la temperatura de operación del VCO, de manera que cada valor de temperatura provoca una frecuencia de oscilación particular. El ajuste lineal, con un factor de correlación r=0.996, es de la forma

$$f = 4585.06 - 18.92 \cdot T \tag{4}$$

donde  $20^{\circ}\text{C} < T < 99^{\circ}\text{C}$ , o equivalentemente

$$T = 243 - 0.053f \tag{5}$$

que es un modelo fácil de implementar en *hardware*; el coeficiente lineal da la pauta para medir la frecuencia en intervalos de 53 ms; la medición de temperatura así realizada requiere un procesamiento digital simple.

## 3.1. Justificación

El transistor MOS presenta un manejo de corriente que es directamente proporcional a la movilidad de portadores,  $\mu_i$ :

$$I_{D} = \begin{cases} \mu_{i} C_{ox} \left(\frac{W}{L}\right)_{i} \left[ (V_{GS,i} - V_{TH,i}) V_{DS,i} - \frac{1}{2} V_{DS,i}^{2} \right], & V_{DS.i} < V_{DSAT,i} \\ \mu_{i} C_{ox} \left(\frac{W}{L}\right)_{i} \frac{(V_{GS,1} - V_{TH,i})^{2}}{2}, & V_{DS,i} \ge V_{DSAT,i} \end{cases}$$

$$(6)$$

donde  $C_{ox}$  es la capacitancia de compuerta por unidad de área,  $V_{GS,i}$ ,  $V_{DS,i}$ ,  $V_{TH,i}$ , y  $V_{DSAT,i}$  son los voltajes de compuerta-fuente, drenaje-fuente, de encendido, y de saturación, respectivamente del transistor de conductividad i, a saber tipo  $\bf p$  o  $\bf n$ ; la aproximación mostrada en (6) corresponde a los modelos analíticos del modelo de simulación spice LEVEL=1. Nótese que una compuerta NOT en operación implica que sus transistores operan desde corte hasta saturación, es decir, en todo modo de operación los efectos térmicos afectan a la movilidad y en consecuencia a la corriente. Esta dependencia térmica se analiza con el siguiente modelo

$$\mu_{eff} = \frac{\mu_{v,i}}{1 + \mu_{v,i} \frac{V_{DS,i}}{v_{sat,i}L_{eff,i}}} \tag{7}$$

donde  $\mu_{eff}$  es la movilidad efectiva de los portadores debida a los campos lateral y vertical del canal,  $v_{sat}$  es la velocidad de saturación,  $L_{eff}$  es la longitud efectiva del canal y  $\mu_v$  es la movilidad debido al campo eléctrico vertical:

$$\mu_v = \mu(T_{\text{nom}}) \left(\frac{T}{T_{\text{nom}}}\right)^{-\alpha} \tag{8}$$

FIGURA 5. Arquitectura para la implementación de (5).

donde  $\mu(T_{\rm nom})$  es la movilidad a la temperatura  $T_{\rm nom}$  (usualmente temperatura ambiente), y  $\alpha$ =1.5 [12]. En particular para silicio, los valores más aceptados para  $\alpha$  son 2.2 y 2.42 para transistores PMOS y NMOS, respectivamente [15]; en la misma referencia pueden hallarse valores para Ge y semiconductores compuestos como GaAs. Puede observarse que la movilidad es inversamente proporcional a la temperatura, con lo cual se justifica por qué a mayor temperatura la frecuencia de oscilación del VCO reduce su valor.

Para propósitos de análisis téngase presente que la corriente  $I_{\mathrm{SHORT}}$  en (3) es la corriente de saturación  $(V_{DS,i}{>}V_{DSAT,i})$  mostrada en (6). Los valores típicos de la movilidad para silicio extrínseco, como función de T, pueden consultarse también en [13].

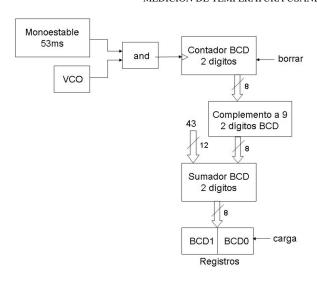

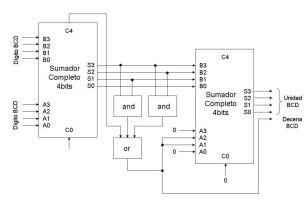

#### 4. Arquitectura

Para la implementación en hardware de (5) se propone realizar un procesamiento de acuerdo a la arquitectura mostrada en la Fig. 5. Es importante señalar que esta arquitectura se implementó con componentes discretos con el único propósito de validar la lectura de temperatura a partir de un procesamiento digital. El principio básico de operación de la arquitectura parte de la definición de un intervalo de 53ms durante el cual se mide (o contabiliza) la frecuencia de oscilación del VCO. Este valor, que deberá ser complementado a 9, será restado del término independiente mostrado en (5); del punto de vista del hardware la operación se realiza con una operación suma. Como las operaciones de conteo y suma se realizan en código BCD, el resultado final es el valor correspondiente a la temperatura en código BCD de 2 dígitos, y la medición será válida para un rango de temperatura de 20° a 99°C con una resolución de 1°C. En la práctica, si se requiriera aumentar la resolución, sólo debe ampliarse la ventana de medición e incrementar dígitos BCD en el procesamiento; para medir décimas de °C se requiere una ventana de 530 ms y un dígito extra BCD.

FIGURA 6. Diagrama de bloques de un sumador de 2 dígitos BCD.

El monoestable mostrado en la Fig. 5 es el circuito responsable de generar el intervalo de 53 ms. Este circuito y una máquina de estados (necesarios para generar las señales de disparo del monoestable, de borrado de los contadores, y de carga de los registros) al implementarse con componentes comerciales permitió evaluar el impacto de la variabilidad del intervalo de tiempo generado al utilizar un base de tiempo basada en componentes con tolerancia, según el fabricante, de  $\pm 0.1\,\%$ ; ese ejercicio permite postular que para variaciones de los componentes, mayores a la descrita, provocan desviaciones en la representación digital de la temperatura que se mide. Por ejemplo, para una variación de hasta  $\pm 1\,\%$  en el intervalo de tiempo se tiene un error promedio equivalente en la temperatura medida de  $\pm 1.8\,^\circ\text{C}$ .

El monoestable, por otro lado, permite habilitar el paso de la frecuencia al contador BCD por medio de una compuerta AND de 2 entradas; el contador BCD de 2 dígitos se construve con 2 celdas de contador BCD de 1 dígito. Cada celda se implementa con flip-flops (FFs) tipo JK desarrollados a partir de FFs tipo D con reset. En esta propuesta se utiliza la metodología de diseño de contadores MOD  $< 2^{M}$  para implementar cada contador BCD de un dígito [14]. En la resta de los sumandos señalada con anterioridad, el complemento a 9 se realiza con 2 celdas de complemento a 9 de 1 dígito BCD basada en un sumador completo de 4 bits [15]. El sumador BCD de 2 dígitos, por otro lado, se implementa con 2 celdas de sumador completo BCD, como la mostrada en la Fig. 6, la cual utiliza 2 sumadores binarios de 4 bits y lógica asociada [15]. Este sumador BCD basa su principio en el hecho de que la suma binaria resultante producirá el dato BCD correcto para las sumas de números decimales en el rango de 0 a 9, mientras que para la suma de números decimales, en el rango de 10 a 19, se deberá adicionar 6 a la suma binaria para producir la suma BCD correcta. Por último, los registros para capturar el valor obtenido de temperatura se implementan con 8 FF tipo D.

Del punto de vista experimental la arquitectura se implementó con circuitos integrados comerciales, SSI y MSI. Un tren de pulsos se obtuvo de un generador de funciones (BK PRECISION, 4011 A) con un ciclo de trabajo del 50%. El periodo de la señal se programó a un valor que representara

un valor de frecuencia válido (ver Fig. 4), y el resultado del procesamiento digital fue desplegado con *displays* de ocho segmentos. Por ejemplo, para una frecuencia (programada) de 4.002 kHz el valor convertido y mostrado fue 30.

Los resultados obtenidos permiten postular que sí es posible usar un elemento sensor que use los elementos básicos de una tecnología digital (por ejemplo un VCO  $\it current-starved$ ), y que es viable realizar el procesamiento digital de las lecturas con circuitos digitales básicos. Consecuentemente todo el sistema sensor puede integrarse en un solo chip, porque esta propuesta no altera el proceso de fabricación de CIs. Sin embargo, más allá de la viabilidad de la integración, el diseño deberá centrarse en el diseño de la arquitectura de procesamiento, y más específicamente en asegurar que el desempeño de los circuitos digitales ocurra dentro de una tolerancia de  $\pm 0.1\,\%$ .

#### 5. Conclusiones

Se ha presentado la caracterización eléctrica de un VCO current-starved como elemento sensor de temperatura, manufacturado en una tecnología CMOS, 0.5  $\mu$ m, pozo N, 5V. La curva característica  $f_{\rm osc}-T$  presenta un rango de temperatura para el cual el desempeño del oscilador muestra una dependencia cuasi-proporcional con T, permitiendo un ajuste

lineal (r=0.996) susceptible de ser implementado en *hardware*. El rango de temperatura propuesto es de 20 a 99°C, la resolución de la medición es de 1°C y la lectura es en código BCD de dos dígitos. La aplicación de este sistema está orientado al sensado de la temperatura interna de los propios circuitos de procesamiento, lo cual permitiría activar algún sistema de ventilación para propósitos de seguridad; por ejemplo la temperatura máxima de un procesador Intel Atom $^{TM}$  N270 es de 90°C [16]. Alternativamente pudiese usarse en algunos sistemas de secado de alimentos, los cuales operan a una temperatura (65 $\pm$ 2) °C.

La simplicidad del *hardware* propuesto, en conjunción con la verificación funcional con elementos discretos, muestra la viabilidad de integrar en un solo chip el elemento sensor y la circuitería digital.

## Agradecimientos

Los autores agradecen las facilidades tecnológicas del programa académico ofertado por MOSIS (www.mosis.org) para la fabricación del chip de prueba, a O.G. Zamora-López y O. Romero-Mayorquin por la validación experimental de la arquitectura digital propuesta, y a los revisores por enriquecer con su opinión la presente contribución.

- 1. F. Sandoval-Ibarra, Rev. Mex. Fís. 47 (2001) 107.

- 2. R. Muller, Microsensors (IEEE Press, New York, 1998).

- M. Sasaki, M. Ikeda y K. Asada, IEEE Trans. on Semiconductor Manufacturing 21 (2008) 201.

- 4. D. Ghai, S.P. Mohanty y E. Kougianos, *IEEE Transactions on Very Large Scale Integration* **17** (2009) 1339

- E. Montoya-Suárez, Diseño y fabricación de bloques básicos para la construcción de un DPLL, (Tesis Maestría, Cinvestav-Guadalajara, Septiembre, 2002).

- 6. M.P. Timko, IEEE J. Solid-State Circuits SC-11 (1975) 784.

- 7. F. Sandoval-Ibarra y E. Hernández-Bernal, J. of Applied Research and Technology 6 (2008) 54.

- 8. Yidong Liu, Microelectronics Journal 42 (2011) 330.

- 9. E. Montoya-Suárez y F. Sandoval-Ibarra, *Proc. of XIII Workshop Iberchip*, (March 14-16, 2007, Lima, Perú).

- K. Lasanen y J. Kostamovaara, IEEE Transactions on Instrumentation and Measurement 57 (2008) 2792.

- 11. B. Datta y W.P. Burleson, *Proc. of the IEEE International SOC Conference* (September 17-20, 2008, Newport Beach, CA)

- D. Foty, Mosfet modeling with spice (Prentice-Hall, New Jersey, 1997).

- S.M. Sze, Physics of semiconductor devices (John Wiley & Sons, Canada, 1981).

- R.J. Tocci, N.S. Widmer y G.L. Moss, Sistemas Digitales (Prentice Hall, 10<sup>a</sup> Edición, 2007).

- T.R. McCalla, Lógica Digital y Diseño de Computadoras (Noriega Editores, 1994.)

- Intel, Mobile Intel Atom Processor N270 Single Core Datasheet www.intel.com, (may 2008).